“`html

تايوان للصناعات المتقدمة (TSMC) عرضت تقنيتها الجديدة من الترانزستورات في اجتماع المؤتمر الدولي للهندسة الكهربائية والإلكترونية (IEDM) في سان فرانسيسكو هذا الأسبوع. وتُعد تقنية نانومتر 2 (N2) أول تجربة للعملاق في صناعة أشباه الموصلات في هندسة ترانزستور جديدة، تُسمى الصفائح النانوية أو بوابة-حول-الكل (gate-all-around).

وتمتلك شركة سامسونج عملية لإنتاج أجهزة مماثلة، ويتوقع كل من إنتل وتايوان للصناعات المتقدمة (TSMC) إنتاجها في عام 2025.

مقارنةً بأحدث عملية تSMC حاليًا (N3 أي 3 نانومتر)، تقدم هذه التقنية الجديدة زيادة في السرعة تصل إلى 15% أو تحسن في كفاءة الطاقة بنسبة تصل إلى 30%، مع زيادة في الكثافة بنسبة 15%.

“`

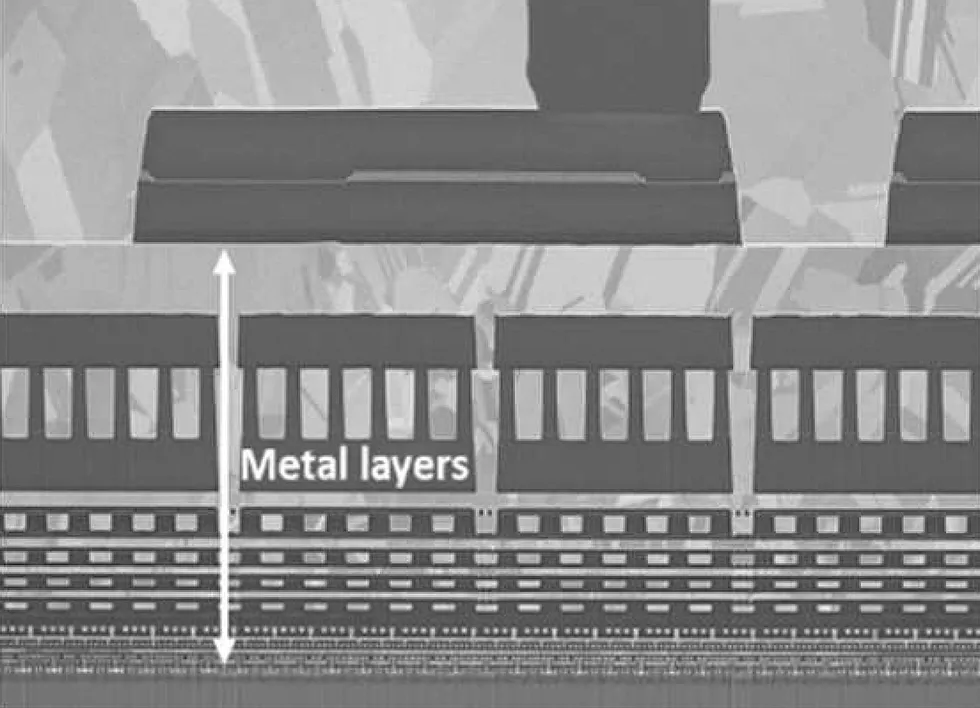

يُعدّ N2 “ثمارَ أكثر من أربع سنوات من العمل”، حسبما صرّح جيفري ياب، نائب رئيس قسم البحث والتطوير والتكنولوجيا المتقدمة في شركة TSMC، للمهندسين في مؤتمر IEDM. يحتوي الترانزستور الحالي، وهو FinFET، على خيوطٍ رأسية من السيليكون في مركزه. أما الترانزستورات التي تستخدم طبقات نانوية أو بوابة تحيط بالكل، فتحتوي على مجموعة من الشرائط الضيقة من السيليكون بدلاً من ذلك.

لا يكمن الفرق فقط في التحكم الأفضل بتدفق التيار عبر الجهاز، بل يُتيح أيضًا للمهندسين إنتاج مجموعة متنوعة أكبر من الأجهزة، من خلال جعل هذه الطبقات النانوية أوسع أو أضيق. فقد كان من الممكن أن يُوفر FinFET هذا التنوع فقط من خلال زيادة عدد الخيوط في الجهاز – مثل جهاز به خيط واحد أو اثنين أو ثلاثة. لكن الطبقات النانوية تُتيح للمصممين خيارات درجات بين هذه القيم، مثل ما يعادل 1.5 خيط أو أي شيء قد يناسب دائرة منطقية معينة بشكل أفضل.

يُسمى هذا التّقنية نانوفليك، وتتيح تقنية شركة TSMC بناء خلايا منطقية مختلفة باستخدام أعرض نانوصفيحة مختلفة على نفس الشّريحة. قد تُشكل الخلايا المنطقية المصنوعة من الأجهزة الضيقة منطقًا عامًا على الشّريحة، بينما تلك ذات النّانوصفيحات الأوسع، القادرة على توليد تيار أكبر والتحويل بشكل أسرع، ستُشكل وحدات المعالجة المركزية.

يُؤثّر مرونة النّانوصفيحة بشكلٍ كبير على ذاكرة SRAM، وهي ذاكرة المعالج الرئيسية على الشّريحة. لم تُقلّل هذه الدّائرة الأساسية، المُكوّنة من 6 ترانزستورات، خلال عدّة أجيال، بنفس سرعة التقنيات المنطقية الأخرى. لكن يبدو أنّ N2 قد كسرت هذا الجمود في التّقليص، مما أسفر عن ما وصفه ياب بأنه أكثر خلية SRAM كثافة حتى الآن: 38 ميجابيت لكل مليمتر مربع، أو زيادة بنسبة 11% عن التّقنية السّابقة، N3. لم تحقق N3 سوى زيادة بنسبة 6% عن سابقتها. يقول ياب: “تحصد ذاكرة SRAM المكاسب المتأصلة من الانتقال إلى بوابة تحيط بكلّ شيء”.

ترانزستورات البوابة الكاملة للمستقبل

في حين قدمت شركة TSMC تفاصيل حول الترانزستور لسنة القادمة، نظرت شركة إنتل إلى مدى قدرة الصناعة على تقليصه. إجابة إنتل: أطول مما كان يُعتقد في البداية.

«إن بنية النانو ورقة هي في الحقيقة الحد الأقصى الأخير لبنية الترانزستور»، قال أشيش أغراوال، عالم تكنولوجيا السيليكون في مجموعة أبحاث المكونات في إنتل، للمهندسين. حتى أجهزة التكميلية للترانزستورات ذات التأثير الميداني (CFET) المستقبلية، التي قد تظهر منتصف ثلاثينيات القرن الحالي، تُصنع من صفائح نانوية. لذا من المهم أن يفهم الباحثون حدودها، كما قال أغراوال.

«لم نصل إلى جدار. هذا ممكن، وهذه هي الدليل… نحن نصنع ترانزستورًا جيدًا حقًا.» — سانجاي ناتاراجان، إنتل

أثبتت إنتل أن الترانزستور ذي طول بوابة 6 نانومتر يعمل بشكل جيد.إنتل

استكشفت إنتل عاملًا حاسمًا في التَصْغِير، وهو طول البوابة، والذي يُمثل المسافة التي يغطيها الباب بين مصدر الترانزستور ومصِرِّه. يتحكم الباب في تدفق التيار عبر الجهاز. يُعدّ تصغير طول البوابة أمرًا بالغ الأهمية لتقليل المسافة الدنيا بين الجهاز والجهاز داخل الدوائر المنطقية القياسية، والتي تُسمّى، لأسباب تاريخية، مُسافة البوليمر المُلامسة (CPP).

قال أغراوال: “يُعتبر تصغير مُسافة البوليمر المُلامسة (CPP) بشكل رئيسي من خلال طول البوابة، لكن من المتوقع أن يتوقف هذا التَصْغِير عند طول بوابة 10 نانومتر”. كان الاعتقاد السائد أن طول البوابة البالغ 10 نانومتر قصير للغاية، مما سيؤدي، من بين مشاكل أخرى، إلى تسرب تيار كبير عبر الجهاز عندما يكون من المفترض أن يكون معزولاً.

قال أغراوال: “لذلك بحثنا في الدفع نحو أقل من 10 نانومتر”. عدلت شركة إنتل الهيكل النموذجي للبوابة المحيطة بالكامل بحيث يمتلك الجهاز ورقة نانوية واحدة فقط تتدفق من خلالها التيار عندما يكون الجهاز قيد التشغيل.

من خلال تقليل سمك هذه الورقة النانوية وتعديل المواد المحيطة بها، تمكن الفريق من إنتاج جهاز ذي أداء مقبول بطول بوابة يبلغ 6 نانومتر فقط وورقة نانوية بسمك 3 نانومتر فقط.

في النهاية، يتوقع الباحثون أن تصل أجهزة السيليكون ذات البوابة المحيطة بالكامل إلى حد محدود من التوسع، لذلك عمل باحثون في إنتل وفي أماكن أخرى على استبدال السيليكون في الورقة النانوية بـ [[LINK15]] أشباه الموصلات ثنائية الأبعاد [[LINK15]] مثل ثنائي كبريتيد الموليبدينوم. لكن النتيجة البالغة 6 نانومتر تعني أن هذه [[LINK16]] أشباه الموصلات ثنائية الأبعاد [[LINK16]] قد لا تكون ضرورية لفترة من الوقت.

«لم نصل إلى جدارٍ»، يقول سانجاي ناتاراجان، نائب الرئيس الأول ومدير عام أبحاث التكنولوجيا في مصنع إنتل. «وهو ممكن، وهذه هي البراهين… نحن نصنع ترانزستورًا جيدًا جدًّا» بطول قناة 6 نانومتر.

من مقالات موقعكم

مقالات ذات صلة على شبكة الإنترنت

المصدر: المصدر